USRP-2974

$23,541.00 USDUSRP-2974 High Performance Embedded SDR, 10 MHz-6 GHz, 160 MHz bandwidth

Provides deterministic control of transceivers using an onboard FPGA and processor for rapidly prototyping high-performance wireless communications systems.

-

Overview

-

Overview

The USRP Software Defined Radio Stand-Alone Device built with an FPGA and an Intel i7 onboard processor which you can provision with NI Linux Real-Time, Linux Fedora, or Linux Ubuntu Real-Time Operating Systems. You can program the onboard processor and FPGA with LabVIEW Communications System Design Suite or use an open-source software workflow to deterministically control your application.

The USRP-2974 is ideal for prototyping a range of advanced research applications that include stand-alone LTE or 802.11 device emulation; Medium Access Control (MAC) algorithm development; multiple input, multiple output (MIMO) systems; heterogeneous networks; LTE relaying; RF compressive sampling; spectrum sensing; cognitive radio; beamforming; and direction finding.

- Stand-alone (embedded) or host-based (network streaming) operation

Demo Video

The registered trademark Linux® is used pursuant to a sublicense from LMI, the exclusive licensee of Linus Torvalds, owner of the mark on a worldwide basis.

-

Features

-

Features

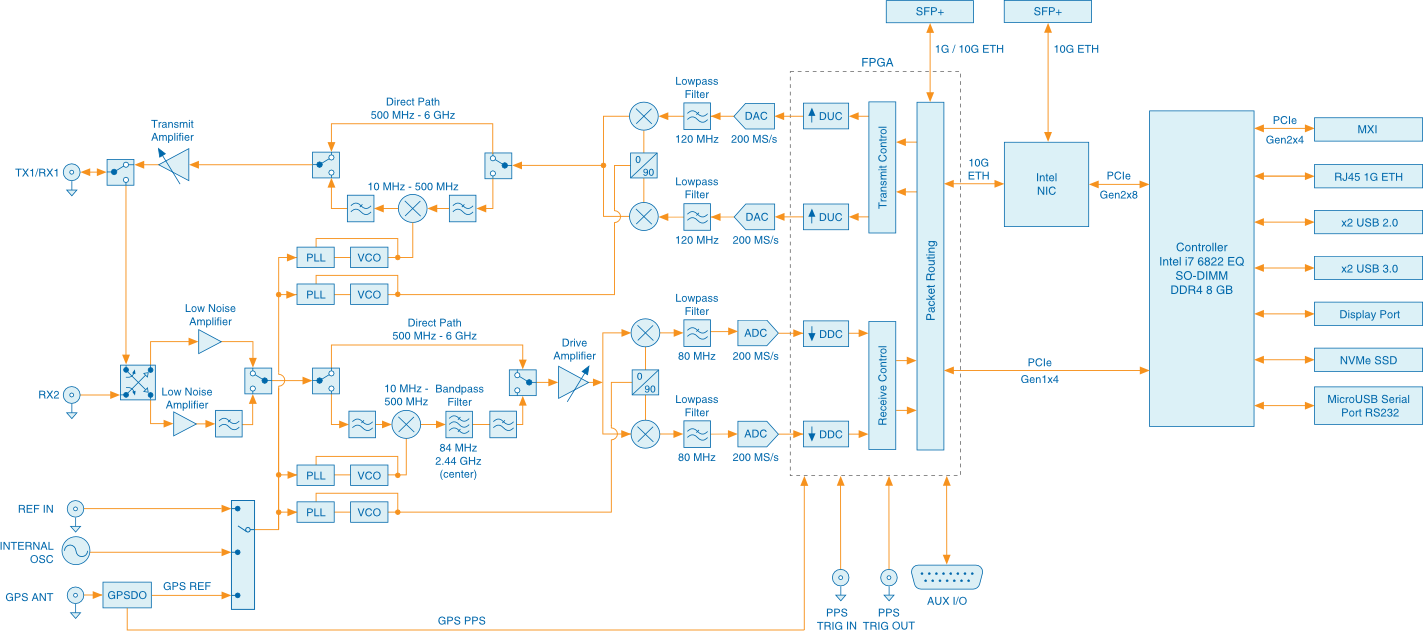

FPGA

- Xilinx Kintex-7 410T

- 14 bit ADC, 16 bit DAC

- Gen1x4 PCIe Connection

- SFP+ High Speed Serial Link

On-board Processor

- x86 onboard processor equipped with NI Linux Real Time OS for deterministic processing

- Intel Core i7 2 GHz Quad Core Processor

- Congatec COM Express Conga-TS170 SoM

- 8 GB DDR4

- MicroUSB to the SoM

- RJ45 (1 GbE)

- PCIe Gen x4

RF

- 2 RX, 2TX

- 10 MHz to 6 GHz extended frequency range

- Up to 160 MHz of instantaneous bandwidth per channel

- RX, TX filter bank

- GPS-Disciplined OCXO

- Clock reference

- PPS time reference

- External RX, TX LO input ports

- Built-in GPSDO

- Interface I/O

Interface I/O

- Two USB 3.0 ports

- Two USB 2.0 ports

- USB 1.0 JTAG

- Display Port

- AUX I/O

- Two SFP+ ports (1 Gigabit Ethernet, 10 Gigabit Ethernet, Aurora)

- PCIe Gen x4

- 1 Gb Ethernet (connection to host)

- Ref In/Out

- PPS In/Out

-

Block Diagram

-

Additional Resources

-

Additional Resources

- USRP-2974 User Manual

- USRP-2974 Hardware Resources

- USRP-2974 Getting Started Guide

- USRP-2974 Front Panel, Back Panel, and LEDs

Kit Contents

- USRP-2974

- 30 dB SMA Attenuator

- SMA Cable

- Power Supply

- Getting Started Guide

Recommended Accessories

Overview

The USRP Software Defined Radio Stand-Alone Device built with an FPGA and an Intel i7 onboard processor which you can provision with NI Linux Real-Time, Linux Fedora, or Linux Ubuntu Real-Time Operating Systems. You can program the onboard processor and FPGA with LabVIEW Communications System Design Suite or use an open-source software workflow to deterministically control your application.

The USRP-2974 is ideal for prototyping a range of advanced research applications that include stand-alone LTE or 802.11 device emulation; Medium Access Control (MAC) algorithm development; multiple input, multiple output (MIMO) systems; heterogeneous networks; LTE relaying; RF compressive sampling; spectrum sensing; cognitive radio; beamforming; and direction finding.

- Stand-alone (embedded) or host-based (network streaming) operation

Demo Video

The registered trademark Linux® is used pursuant to a sublicense from LMI, the exclusive licensee of Linus Torvalds, owner of the mark on a worldwide basis.

Features

FPGA

- Xilinx Kintex-7 410T

- 14 bit ADC, 16 bit DAC

- Gen1x4 PCIe Connection

- SFP+ High Speed Serial Link

On-board Processor

- x86 onboard processor equipped with NI Linux Real Time OS for deterministic processing

- Intel Core i7 2 GHz Quad Core Processor

- Congatec COM Express Conga-TS170 SoM

- 8 GB DDR4

- MicroUSB to the SoM

- RJ45 (1 GbE)

- PCIe Gen x4

RF

- 2 RX, 2TX

- 10 MHz to 6 GHz extended frequency range

- Up to 160 MHz of instantaneous bandwidth per channel

- RX, TX filter bank

- GPS-Disciplined OCXO

- Clock reference

- PPS time reference

- External RX, TX LO input ports

- Built-in GPSDO

- Interface I/O

Interface I/O

- Two USB 3.0 ports

- Two USB 2.0 ports

- USB 1.0 JTAG

- Display Port

- AUX I/O

- Two SFP+ ports (1 Gigabit Ethernet, 10 Gigabit Ethernet, Aurora)

- PCIe Gen x4

- 1 Gb Ethernet (connection to host)

- Ref In/Out

- PPS In/Out

Additional Resources

- USRP-2974 User Manual

- USRP-2974 Hardware Resources

- USRP-2974 Getting Started Guide

- USRP-2974 Front Panel, Back Panel, and LEDs

Kit Contents

- USRP-2974

- 30 dB SMA Attenuator

- SMA Cable

- Power Supply

- Getting Started Guide

Recommended Accessories